Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Internetseiten nicht korrekt angezeigt werden.

Du solltest ein Update durchführen oder einen alternativen Browser verwenden.

Du solltest ein Update durchführen oder einen alternativen Browser verwenden.

AMD RED BIOS EDITOR und MorePowerTool - BIOS-Einträge anpassen, optimieren und noch stabiler übertakten | Navi unlimited

- Themenstarter Igor Wallossek

- Beginndatum

Veii

Veteran

- Mitglied seit

- Okt 24, 2021

- Beiträge

- 187

- Bewertungspunkte

- 214

- Punkte

- 44

Mit DFLL Änderungen bzw dem Undervolt, entfällt TDC Score Throttle "Trick"Hmja. Du bist m. W. auch der Einzige, bei dem "TDC Drossel" positives bewirkt.

Er ist nur nützlich um Fabric crashes zu verhindern , und weiterhin um etwas Frequency rauszuholen. Aber generell ist das ne overvoltage Sache und ein PPT limit später eher nützlich. Den ein TDC throttle verhindert zwar crashes, aber eigentlich verringert es VID requests. Genau so gut geht es mit dem Voltage Slider oder einfach eine tiefere Curve

Zuletzt bearbeitet

:

That would be me, myself and i.MPT Team

I put everything now in "more" tab, extra dialog window.Do you think it's still a good idea for that "Dfll model select"?

..and there is a lot more i put there, not just the perpart-stuff:

I still have to test a little, will do that tomorrow. If i find no bugs release will be whenever igor finds the time. It is getting to eat my time lately..

RX480

Urgestein

- Mitglied seit

- Feb 13, 2020

- Beiträge

- 1.887

- Bewertungspunkte

- 879

- Punkte

- 114

Ist Das aus so nem 6950-Bios?

edit: jetzt seh ich´s bei Veii , ... ist aus nem 6900XTXH-Bios

... zumindestens erstmal beruhigend, das die Kurven 1+2+3 und 4+5 jeweils identisch sind

(hatte Das nach den Posts von Veii differenzierter/sprunghafter befürchtet)

... kann mir gar net vorstellen das normal "piecewise linear" dann "unruhiger" sein soll, ... maximal am Übergang Kurve 3 zu 4

--> evtl. dann bei den Sparsettings für Bereich <4 oder >3 entscheiden, hinsichtlich W+V+Mhz, also irgendwo zw. 200 und 250W@6900xtx

(die Grenze müsste dann ja bei ca. eff.2300MHz liegen mit dem 6950er, welches redF jetzt drin hat)

edit: jetzt seh ich´s bei Veii , ... ist aus nem 6900XTXH-Bios

... zumindestens erstmal beruhigend, das die Kurven 1+2+3 und 4+5 jeweils identisch sind

(hatte Das nach den Posts von Veii differenzierter/sprunghafter befürchtet)

... kann mir gar net vorstellen das normal "piecewise linear" dann "unruhiger" sein soll, ... maximal am Übergang Kurve 3 zu 4

--> evtl. dann bei den Sparsettings für Bereich <4 oder >3 entscheiden, hinsichtlich W+V+Mhz, also irgendwo zw. 200 und 250W@6900xtx

(die Grenze müsste dann ja bei ca. eff.2300MHz liegen mit dem 6950er, welches redF jetzt drin hat)

Zuletzt bearbeitet

:

Veii

Veteran

- Mitglied seit

- Okt 24, 2021

- Beiträge

- 187

- Bewertungspunkte

- 214

- Punkte

- 44

(hatte Das nach den Posts von Veii differenzierter/sprunghafter befürchtet)

KXTX

6950 vs 6800 - Linear

6700-6750XT PP-PW-Quadratic

Don't underestimate what an VertexPoint (B) change does

The first 3 are similar

usually the P0 and P4 stand out

P1 & P2 are similar

P3 and P4 show then binning changes

It's less about the similarity, but about the curvature itself

You can clearly see on Constant (C) that the Y height point on KXTX is very different between those

They are not the same curve

It has to be, anything else is lazy approachYou can clearly see on Constant (C) that the Y height point on KXTX is very different between those

Although using same Axis is lazy approach too, but i wont judge

6800-6900 XT(X) card is the earliest with least love. 6750XT is the one that got most of the love. 6950 just barely followed XTXH OC REF, they are similar

Barebones XTXH is "booring" too , didn't get much tuning love

Zuletzt bearbeitet

:

Veii

Veteran

- Mitglied seit

- Okt 24, 2021

- Beiträge

- 187

- Bewertungspunkte

- 214

- Punkte

- 44

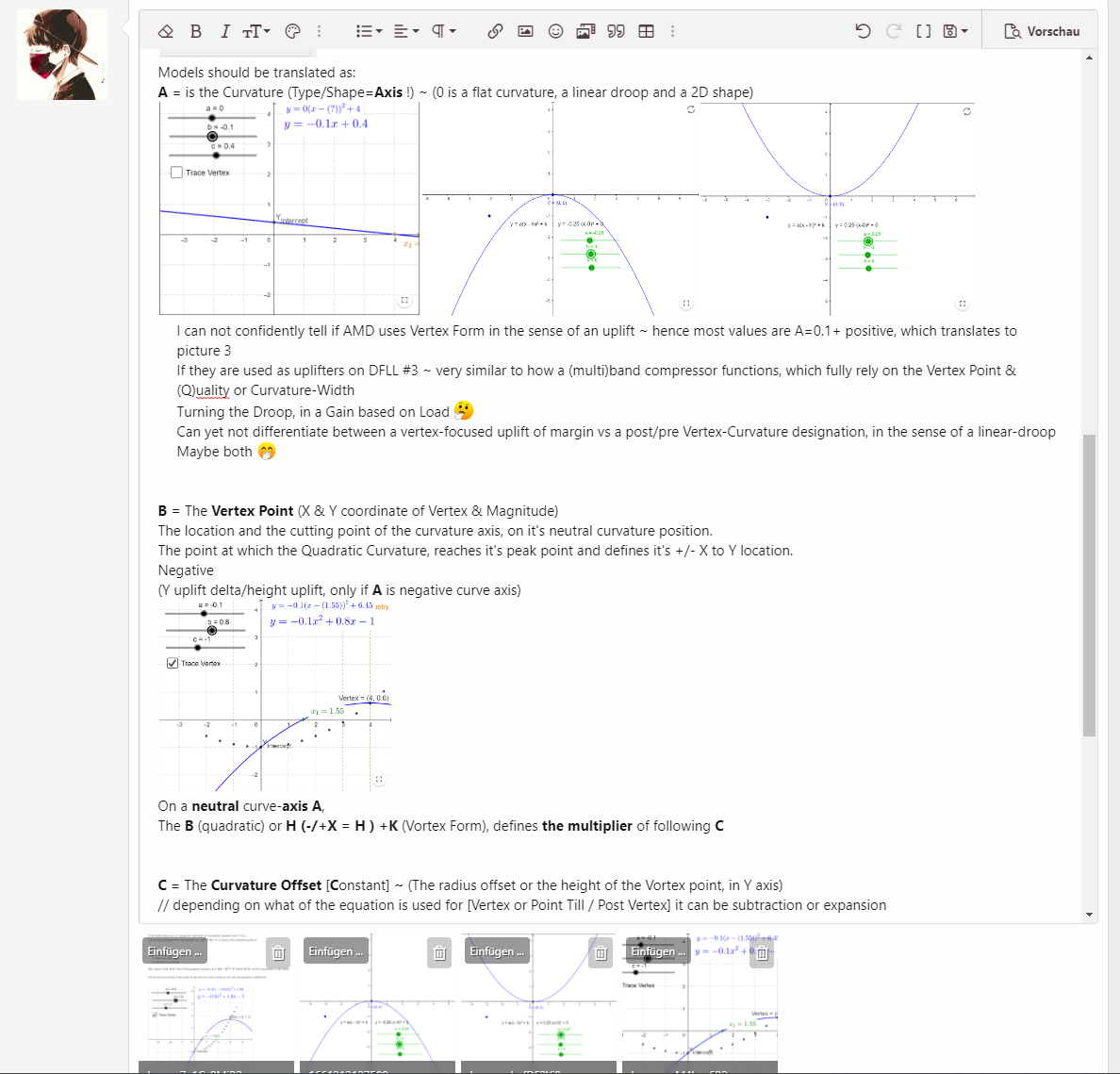

what means "c" ?

this is different in every curve

I was about to write something 4 weeks ago as correction post, but took 1-2 days and igorslab "save draft" option actually erased the whole post

A is the axis of the curvature

B is the middle-vertex point, of the curvature

C is the constant or +/- Y height of the curvature (height defines voltage)

I'll write a clear post once everything is perfectly known, and likely at the end of the Month

(busy, there is a lot to do still & RDNA3 is nearby)

Soo we can work with curves, Yuri finishes his job, i get my credits and people here have time explore them till/start of the next month

Try to google "quadratic function" & "Vertex Form" function. I learned it that way.

It's "bothersome" to imagine numbers and values

But as those are not voltage droops, they don't follow 6.25mV stepping and are more granular.

Hopefully we can make a visual plotter for this someday

EDIT: Picture is old and gladly never send. I lacked info

I can write this clearer now, but curve description stays

Zuletzt bearbeitet

:

Nice )I put everything now in "more" tab, extra dialog window.

..and there is a lot more i put there, not just the perpart-stuff:

@Veii

Ok... I've made a couple of benches when managed to run 6800XT with the pp_table from 6950 liquid devil bios posted by RX480.

All tests made @ PPT 347W TDC 347A, MemClk 2100, DS off. Scores below for the PP_PWL and PWL mode respectively:

Superposition (Fmax 2750, Vdd offset 1080)

11,943 vs 12,077

Timespy (Fmax 2670, Vdd offset 1070)

22,404 vs 22,601

My verdict - not worth it.

Zuletzt bearbeitet

:

I thought everybody was used to it(had feared that after Veii’s posts would be more differentiated/erratic)

Veii

Veteran

- Mitglied seit

- Okt 24, 2021

- Beiträge

- 187

- Bewertungspunkte

- 214

- Punkte

- 44

KXTX is still very overvolted ~ at least 100mVMy verdict - not worth it.

https://github.com/kruzer/poclmembench grab this and start benching mem (1024) and L$ 128 size

(-r 1000 -s 128) & (-r 1000 -s 1024) // too low and variable is too big

You'll find some interesting results ... oh also branch prediction hits after some time.

There is a big rabbit hole

It's the usual zen issue of VID requests exceeding FIT max voltage and package throttling - now also included SOC in it

Long posts, i try to avoidI thought everybody was used to it

LUXX and Igorslab is not used to it.

Long technical posts even less

Glad to have you here tho~

from the omitted

I mean "Part" in the "per-part" term means a piece of silicon wafer, i.e. single monolithic chip, and in the above context - unique fused avfs dataPer Part is mostly Navi1x Quadratic Curvature but more granular in Voltage ranges.

Unless you mean ASIC (SKU) ?

I've asked which settings exactly in a 6800XT PP Table, aside from 5 DfllDroopInt's (a,b,c) one should modify to make it work, or setting these "a,b,c" VF points is enough?93% clear on DFLL & 78% on whole Navi

Zuletzt bearbeitet

:

What was the voltage and max PPT in this run? Did you override Vmax?23,949 with 22.8.2 and Win11

My ref. chip seems at the edge of stability even at Fmax 2750. This is with the Fmax 2720 and 408W PPT limit (1200mv Vmax)

& 2750 @414W

Anhänge

Zuletzt bearbeitet

:

RedF

Urgestein

1,34V 500Watt ^^What was the voltage and max PPT in this run? Did you override Vmax?

My ref. chip seems not to be stable enough even at Fmax 2750. This is with the Fmax 2720 and 408W PPT limit (1200mv Vmax)

The guys wanted to see something extreme.

excellent score !!!

OMG Excellent Score

You Have Excelent chip Both 5800x3d and 6800xt

Veii

Veteran

- Mitglied seit

- Okt 24, 2021

- Beiträge

- 187

- Bewertungspunkte

- 214

- Punkte

- 44

@hellm you got a bug on .17 release

Section 0x0742 , 0x0746 & 0x074a

A, B, C changes are applying but not visible read out in software

So far all is fine

There is a potential issue with:

0x0810 & 0x0812 not always applying, somewhy. But couple of attempts and a full reboot & it works

Keep up the hard work

EDIT:

Also lovely

EDIT2:

Let me know once that is fixed so i can redownload.

Alternatively, come over to PM~

@PJVol i'll answer later with correct tutorial

It's bit too early, else yes main ones

I suggest to zero out DcBTCmin/max both, at first. Redo curve on light 3D load , low amperage (heaven is one)

Watch FPS drops to stay always above 60 and work with VID.

Once that is done increase DcBtcMax in 6 steps, 100 is max. It's PSM. Is BtcMax does not adapt automatically, add BtcMin to force it run X "scalar"

Alternatively reverse idea, drop PSM Voltage slider and that cuts down Btc margin. Check how much voltage headroom you have. I got 150mV cut.

I would leave around 50mV delta, for DcBtc to do it's thing. Timespy is high amperage load and needs more voltage.

Btc does adapt that, but for clean curve generation, zero them out first

EDIT3:

Ahh i know what happens @hellm

You reversed GFX & SOC field

Functionality is correct but both override fiels are "visually" swapped. Readout is swapped, functionality in corresponding field is correct

Section 0x0742 , 0x0746 & 0x074a

A, B, C changes are applying but not visible read out in software

So far all is fine

There is a potential issue with:

0x0810 & 0x0812 not always applying, somewhy. But couple of attempts and a full reboot & it works

Keep up the hard work

EDIT:

Also lovely

EDIT2:

Let me know once that is fixed so i can redownload.

Alternatively, come over to PM~

@PJVol i'll answer later with correct tutorial

It's bit too early, else yes main ones

I suggest to zero out DcBTCmin/max both, at first. Redo curve on light 3D load , low amperage (heaven is one)

Watch FPS drops to stay always above 60 and work with VID.

Once that is done increase DcBtcMax in 6 steps, 100 is max. It's PSM. Is BtcMax does not adapt automatically, add BtcMin to force it run X "scalar"

Alternatively reverse idea, drop PSM Voltage slider and that cuts down Btc margin. Check how much voltage headroom you have. I got 150mV cut.

I would leave around 50mV delta, for DcBtc to do it's thing. Timespy is high amperage load and needs more voltage.

Btc does adapt that, but for clean curve generation, zero them out first

EDIT3:

Ahh i know what happens @hellm

You reversed GFX & SOC field

Functionality is correct but both override fiels are "visually" swapped. Readout is swapped, functionality in corresponding field is correct

Zuletzt bearbeitet

:

thx

Yes the bug was 2x AVFS GFX read out, the writing part was right; so SOC settings got overwritten with GFX part, if you hadn't changed them. I fixed it now, should be online by tomorrow morning.

VcBtcVminT0, VcBtcFixedVminAgingOffset and VcBtcVmin2PsmDegrationGb are Q2 voltage values, so they are rounded up/down. Should work.

Yes the bug was 2x AVFS GFX read out, the writing part was right; so SOC settings got overwritten with GFX part, if you hadn't changed them. I fixed it now, should be online by tomorrow morning.

VcBtcVminT0, VcBtcFixedVminAgingOffset and VcBtcVmin2PsmDegrationGb are Q2 voltage values, so they are rounded up/down. Should work.

Veii

Veteran

- Mitglied seit

- Okt 24, 2021

- Beiträge

- 187

- Bewertungspunkte

- 214

- Punkte

- 44

again, thx

some sort of typo, read function is basically a copy of set function, only that 1 letter was changed, SetDlgItemTextW to GetDlgItemTextW; and here it still was the set function for 2 to 5, so every time you hit the OK button it just changed it to the value it was before.

Again, fixed version will be online by tomorrow morning for the official release.

some sort of typo, read function is basically a copy of set function, only that 1 letter was changed, SetDlgItemTextW to GetDlgItemTextW; and here it still was the set function for 2 to 5, so every time you hit the OK button it just changed it to the value it was before.

Again, fixed version will be online by tomorrow morning for the official release.