Gastspiel auf AM5

Alternativ könnte man es so machen wie AMD, wo das RAM-Training keine Stimmungsschwankungen hat und DDR5 auch am Grenzbereich des IMC reproduzierbar trainiert. Ich habe mir den Spaß mal gemacht und das Corsair Dominator Titantium Kit mit DDR5-8000 XMP Profil einfach auf ein AM5 Board gesteckt. Obwohl XMP ja eigentlich für Intel Plattformen gedacht ist und wiederum EXPO für AMD konzipiert ist, technisch steckt hinter beiden Standards die gleiche Lösung mit den gleichen vorgegebenen RAM-Timings. Und genau deswegen kann das Asus Crosshair X670E Gene auch problemlos das XMP-Profil via „DOCP“ laden. Hierbei handelt es sich auch um ein 2-DIMM Board und quasi das Asus Äquivalent für AM5 zum Z790 Apex für LGA1700. Wichtig ist dabei nur, dass ein halbwegs aktuelles BIOS / AGESA zum Einsatz kommt, dass die hohen Taktraten im 1:2 Modus unterstützt, wie hier das 1807 Release.

Und siehe da, es ist einfach immer stabil! Auch AMD hat „MRC Fastboot“, nur dass es hier „Memory Context Restore“ heißt. Wenn man dies deaktiviert, trainiert das System bei jedem Neustart neu und man kann so durch Stresstests mit zwischenzeitlichen Reboots die Verlässlichkeit des RAM-Trainings evaluieren. Auch werden auf dieser Plattform alle Timings respektiert, inklusive tWR, was Asus ja leider auf dem Intel Board nicht tut. Natürlich sind auch hier die Subtimings vieeel zu locker, wie bei Intel CPUs, und die Performance deswegen nicht so prickeln wie sie bei diesem Takt sein könnte. Aber immerhin ist das System reproduzierbar stabil und das ist ja überhaupt erst die Voraussetzung, dass wir uns über Performance-Tuning Gedanken machen können!

Inwiefern nun DDR5-8000 auf AM5 Sinn ergibt, ist wieder eine eigene Debatte, vor allem mit einer X3D CPU wie hier. FCLK 2000, UCLK 2000, MCLK 4000 liest sich zwar ganz hübsch und wenn man an Ryzen 5000 Zeiten denkt, könnte man durch „synchrone“ Taktraten mehr Performance erwarten, aber leider ist bei Ryzen 7000 leider das Infinity Fabric ein zu großer (kleiner) Flaschenhals, als dass die RAM-Bandbreite voll genutzt werden können. AMD hat ein Flaschenhals-Problem zwischen Kernen und RAM-Controller. Intel hat ein Stimmungsschwankungs-Problem zwischen RAM-Controller und RAM. Wenn man sich nur das beste aus beiden Welten nehmen einfach könnte…

Was ich mit dem Gastspiel auf AM5 zeigen will: Das Stabilitäts-Problem liegt hier nicht an Corsairs Dominator Titanium RGB DDR5-8000 Kit. Kombiniert man dieses nämlich mit einer AMD-CPU, lassen sich auch 8000 Mbps tatsächlich reproduzierbar und stabil betreiben. Mit einer Intel Plattform ist Stabilität bei solch hohen Taktraten leider oft Glücksspiel. Diese Problematik gibt es schon seit den ersten DDR5-CPUs der 12ten Generation, aber mit Fortschritten in der DRAM-Technik und zunehmenden Taktraten wird das Thema immer brisanter. Vermutlich ist auch genau das der Grund, warum Corsair das Kit nicht als DDR5-8200 bewirbt, obwohl das XMP-Profil dafür schon im SPD enthalten ist. Es würde mich nicht überraschen, wenn man sich im R&D Department der Hersteller diesbezüglich schon länger den Kopf zerbricht.

Overclocking

DDR5-7800 habe ich nun als effektives Limit meines Intel Testsystems identifiziert und auf Basis dessen die Timings angezogen und die Spannung etwas erhöht. 1,6 V VDD ist die einzige erhöhte Spannung; sogar VDDQ, VDD2 und CPU VDDQ können unverändert zum XMP-Profil bleiben, bei 1,4 V. Dass die VDD- und VDDQ-Spannungen dann nicht mehr synchron sind, ist kein Problem, solange die Differenz nicht mehr als 300 mV beträgt, jedenfalls laut offiziellen Dokumentationen von DDR5-Herstellern.

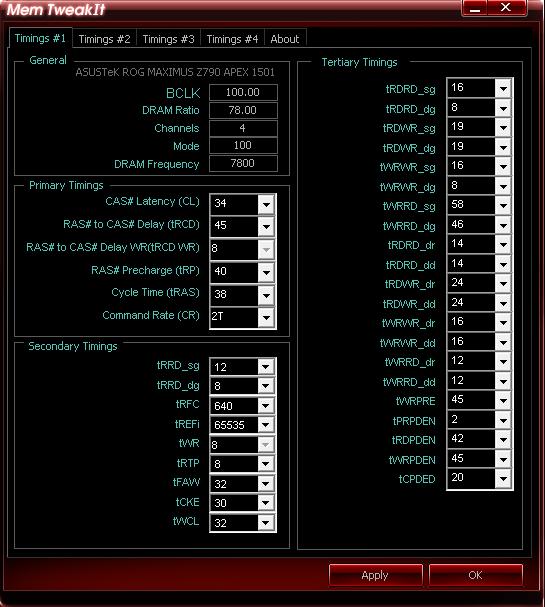

tCL lässt sich nun durch die zusätzliche VDD-Spannung auf 34 senken. tCL 32 habe ich auch probiert, aber dafür bräuchte man wohl > 1,7 V und das war mir dann zu extrem, auch mit einem Lüfter auf den Modulen. Die restlichen Timings lassen sich Hynix-typisch deutlich straffen, wie z.B. tRDRD_sg/dg und tWRWR_sg/dg auf jeweils 16/8. Diese erhöhen vor allem die Bandbreite deutlich und funktionieren effektiv immer bei SK Hynix basierten DDR5-Kits. Teilweise kann man diese sogar noch weiter anziehen, aber oft lässt sich dann keinen Performance Unterschied mehr messen. Auch tRRD_sg/dg und tFAW lassen sich deutlich straffen, allerdings haben die 24 Gbit ICs scheinbar einen Mindestwert von tRRD_sg 12, während 16 Gbit ICs oft einen Wert von 8 stabil betreiben konnten.

tCKE habe ich ehrlichgesagt nach Wochen des Testens schlichtweg übersehen, aber Performance-technisch ist das Timing ohnehin effektiv irrelevant. tRFC_pb zeigt MemTweakIt nicht auf der ersten Seite an – dieses Timing steht auf 576. Für eine vollständige Aufführung der angepassten Timings, guckt bitte auf die Screenshots.

Allgemein fällt auf, dass SK Hynix 24 Gbit M-Die etwas lockerere Timings als 16 Gbit A-Die bei der selben Taktrate fahren muss. Trotzdem gibt es momentan keinen anderen IC-Hersteller der auch nur annähernd der beim Verhältnis von Taktrate zu Timings hier annähernd mithalten könnte.

49 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Veteran

Urgestein

Veteran

Veteran

Veteran

Urgestein

Urgestein

Urgestein

Urgestein

Veteran

Urgestein

Veteran

Urgestein

Urgestein

Veteran

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →