Der gerade beschriebe Phison PS5019-E19T ist mit einer breiten Palette von Flash-Speichervarianten kompatibel und unterstützt moderne NAND-Chips mit 1200-MHz-Schnittstelle. Und weil er so schön kompatibel ist, kann man als Anbieter einer günstigen NVMe SSD auch Microns neuestes 176-Layer-TLC-3D-NAND (Codename B47R) damit verwenden. So enthält die von mir getestete MSI Spatium M450 zwei IABHG94AYA-Chips mit jeweils acht 512-Gigabit-TLC-3D-NAND-Blöcken im Inneren.

Der noch recht neue 176-Layer-Flash von Micron ist übrigens die erste echte Eigenentwicklung von Micron nach der Trennung von Intel. Dieser Speicher unterscheidet sich im inneren Aufbau auch sehr deutlich von den Produkten aller anderen Hersteller. Die Zellstruktur des Micron-NANDs setzt dabei auf Replacement Gate, was am Ende eine Kreuzung aus Floating-Gate- und Charge-Trap-Technologien darstellt. Micron ersetzt bei diesem NAND das Polysilizium im Gate-Material durch Metall und wechselte zu einem anderen Verfahren für das Ätzen des vertikalen zylindrischen Kanals, woraus ein vergrößerter Durchmesser resultiert.

Darüber hinaus ist in der Struktur des Micron-Speichers eine nichtleitende Schicht aus Siliziumnitrid eingebracht worden, in der Daten gespeichert werden können. Diese Schicht reduziert zudem recht wirkungsvoll auch die gegenseitige Beeinflussung der Zellen in so einem einem vertikalen Stapel. Wie das mit dem Stapel so funktioniert, erläutert ein Video von Micron, dass so trivial daherkommt, dass es schon wieder sehenswert ist. Das will ich Euch natürlich nicht vorenthalten:

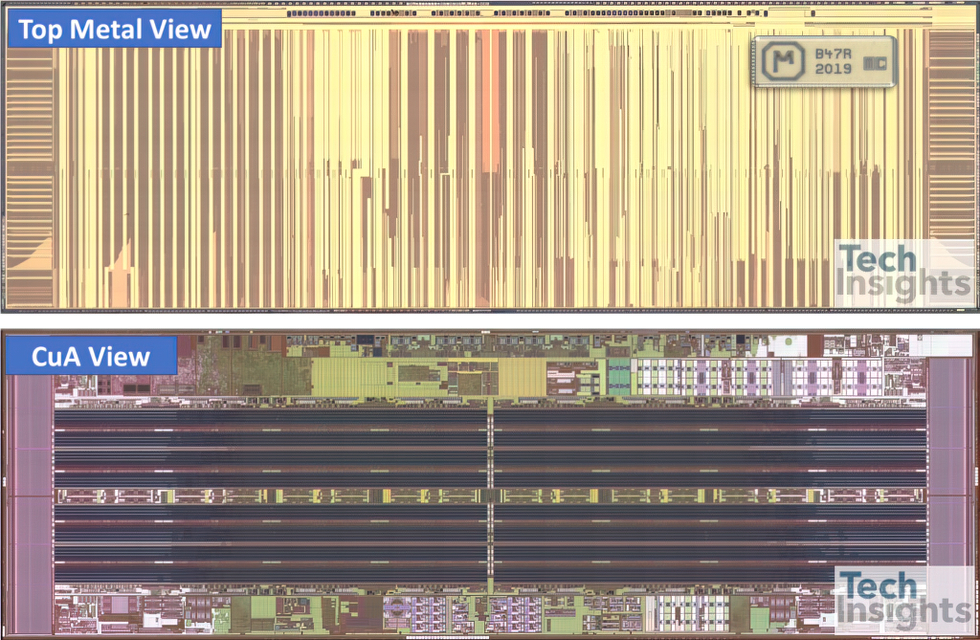

Natürlich können wir auch noch etwas weiter ins Detail gehen. Die nächste Abbildung zeigt einen Chip mit Blick auf die Metalloberseite, einen Chip mit Blick auf die CMOS-Schaltkreise (CuA) und die Markierungen des B47R Chips. Im Vergleich zum älteren B37R TLC-Die konnte die Chipgröße aufgrund der höheren Zelldichte, der größeren Anzahl von 3D-NAND-Zellen und der effektiven Skalierung des Designs um satte 25 % verringert werden. Der B47R ist nunmehr nach dem B37R die zweite Generation der CTF-Struktur von Micron.

Die Höhe des NAND-Zellen-Arrays (zum Vergleich: die Höhe vom Selektor auf der Source-Seite bis zum BL) beträgt jetzt mehr als 11 µm. Die Gesamtzahl der Gatter, einschließlich Selektoren (STs) und Dummy-Word-Lines (DWLs) pro vertikalem NAND-Strang beträgt 195, so genannte 195T, was die höchste jemals bei 3D-NAND erreichte Anzahl darstellt. Sie setzen auf die Double-Stack-Architektur, den Replacement-Gate-Prozess, Charger-Trap-Nitrid (CTN) und CMOS-under-Array (CuA)-Techniken. Die Bitdichte erreicht 10,273 Gb/mm2 für den 512Gb TLC-Die.

So konnte man am Schluss auch Reihe positiver Effekte zu erzielen, denn es war möglich die Geschwindigkeit der Programmierzellen zu steigern, ihre Stabilität zu erhöhen, den Stromverbrauch zu senken und gleichzeitig auch die Zuverlässigkeit der Datenspeicherung zu verbessern. Letztendlich macht Microns aus 176 Schichten (Layer) bestehender TLC-3D-NAND damit den nächsten Schritt in der 3D-Flash-Technologie im Allgemeinen. Und in Bezug auf die Leistung behauptet Micron, dass der neue Speicher die Lese- und Schreiblatenz im Vergleich zum 96-Layer-Speicher der vorherigen Generation um etwa 35 % reduziert hat. Nun ja…

22 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Mitglied

Urgestein

1

Mitglied

Mitglied

1

Veteran

Moderator

Mitglied

1

1

Moderator

Veteran

1

Mitglied

Mitglied

Mitglied

Alle Kommentare lesen unter igor´sLAB Community →