“Adaptive” OC – 5.7 GHz single-core boost

Of course, the Unify-X also supports Adaptive OC, where the cores can clock at different rates and request different voltages depending on the workload. This is where the parameters AC_LL, DC_LL and LLC come into play, which are responsible for interpreting the voltage requested by the CPU (SVID). Hereby we also intervene deeply into the PCU (Power Control Unit) of the CPU at the same time and try to get the maximum clock / voltage out in all situations.

The Unify-X has relatively low LLC resistances, so the setting with most Vdroop LLC 8 can be roughly compared to LLC level 2-3 on the Asus Z690 Apex. As a result, a bit more of the requested voltage always arrives at the CPU anyway. Of course, this initially increases stability, but also provides more waste heat, power consumption and, in some situations, instability again. With the LLC 8 setting, I configured two adaptive OC settings, one with P and E cores active and one with only P cores but AVX512. Since the latter has a hard multiplier limit at x51 from Intel, we have to trick it a bit here, but more about that in a moment.

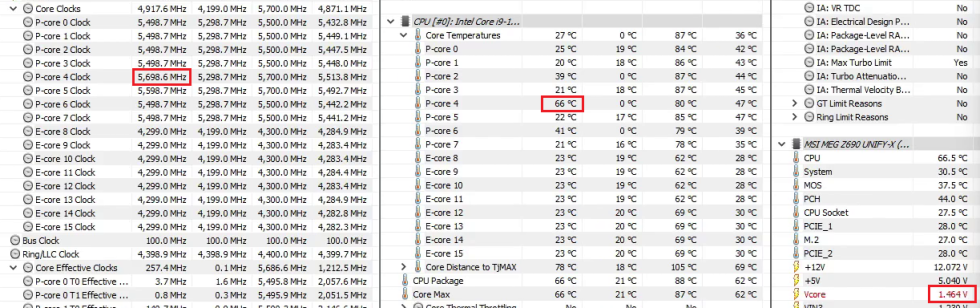

5.3 GHz on all P cores and up to 5.7 GHz on a single P core with voltages under load of 1.26 to 1.45 V VCC Sense are set here in the end. The E-cores are a bit less variable with 4.2 to 4.3 GHz and the cache sits statically at 4.4 GHz. Although all cores and the cache have their own SVID with which they request voltage, the highest one always wins in the end, so effectively the P cores are decisive for the voltage supplied by the VRM.

The idle voltage is up to 1.5 V, which might sound like a lot at first. On the one hand, this is only in states without load, thus low current, power consumption and waste heat, and on the other hand, the Unify-X measures the voltage with “VCC Sense”, i.e. before the CPU die, so that the voltage arriving there is another 20-60 mV lower. In other words, I wouldn’t have any longevity or degradation concerns about using this setting on a daily basis.

Under load in Prime95 with “Small FFT” preset and AVX2, the warmest P-cores reach just under 90 °C, which is still completely within reason for the Alder Lake CPUs that tend to run very warm. The fewer cores are active, the higher they can afford to clock, and even if they demand a higher voltage, they still run significantly cooler than when all neighboring cores also emit heat. Adaptive OC makes sense in exactly such situations, which is basically just a tuned Turbo Boost from Intel, where headroom in voltage and temperature would otherwise remain unused in a static OC.

The important settings in the BIOS for this are the LLC of the VRM on level 8, as well as “Light Load Control” in the advanced CPU settings. DC Loadline 125 corresponds to the approximately determined 1.25 mOhm of the LLC, whereby DL_LL is only needed the read back correctly VID and power consumption. Important for the stability is the AC loadline, which I set here to the lowest value 1, i.e. 0.01 mOhm. The reason for this is that my particular CPU is effectively too efficient for the board, and even the very lowest voltage that can be set like this still runs stably. For most CPUs with conventional cooling, a value of 20-40 with LLC8 would be recommended here.

It is important to disable IA CEP (Current Excursion Protection) for the “Undervolting” to work. This is actually a protection mechanism, but it also triggers when the voltage is supposedly too low and would throttle the CPU under load. This would then show up in very low temperatures and power consumption under load, or as a low “effective clock rate” in current versions of HWinfo, where the actual clock rate is still fully present. Now all that remains is the relatively simple tuning of the frequency depending on the number of utilized P or E cores and the adjustment of the V/F points.

Here again, the board has a bit too little leeway to tune my CPU to the real voltage minimum (admittedly complaining on a high level). Accordingly, I set an offset of -0.3 V for the multiplier x48 and + 0.125 V for the multiplier x57 (the highest set P-core clock). Since the set clock rates of 5.3 GHz to 5.7 GHz are between these points, the board simply interpolates the necessary voltage linearly with the PCU.

Unfortunately, the clock rates for 1 and 2 utilized cores only apply to the CPU’s “favored cores” on this motherboard, so only P-core 4 and 5 get over 5.5 GHz in clock. These preferred cores are predefined by Intel for every CPU and unfortunately, the maximum clock limit of individual cores cannot be adjusted in the BIOS of the Unify-X in “Turbo Ratio” mode. Perhaps there could be a BIOS update for this.

The same principle can now be applied to the P cores alone and combined with AVX-512. Since Intel pulls the handbrake here with the x51 multiplier, we have to make do with BCLK on top of that. Since the CPU’s BCLK only affects the CPU cores, cache and RAM in Alder Lake and the PCIe and SATA buses are decoupled, such a configuration is also conceivable for daily use.

Unfortunately, overclocking with BCLK has the effect that the VID voltage requested by the CPU is corrected upwards (BCLK adaptive voltage). This is a feature of Intel, which effectively forces the minimum voltage to be raised to a minimum floor, even if the CPU doesn’t actually need it. The consequence is “too much” voltage when all cores are loaded and thus unnecessarily high temperatures and power consumption. MSI strictly adheres to the Intel specification here, and boards like the Z690 Apex can only get around this because Asus effectively overrides it – but more on that in the upcoming review of that motherboard.

Now it should be mentioned that this is a CPU with above-average quality in the cores (SP93 at Asus) and it is also operated with direct-die cooling. But such an Adaptive OC can also be used sensibly with normal cooling and average CPUs, and the Unify-X offers all options for this. However, these settings should of course be used with caution, as a too high value selected for the AC_LL, V/F offsets or an LLC with too little resistance can result in too much core voltage.

5 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Veteran

Veteran

Veteran

Veteran

Alle Kommentare lesen unter igor´sLAB Community →