MC SP and its insignificance

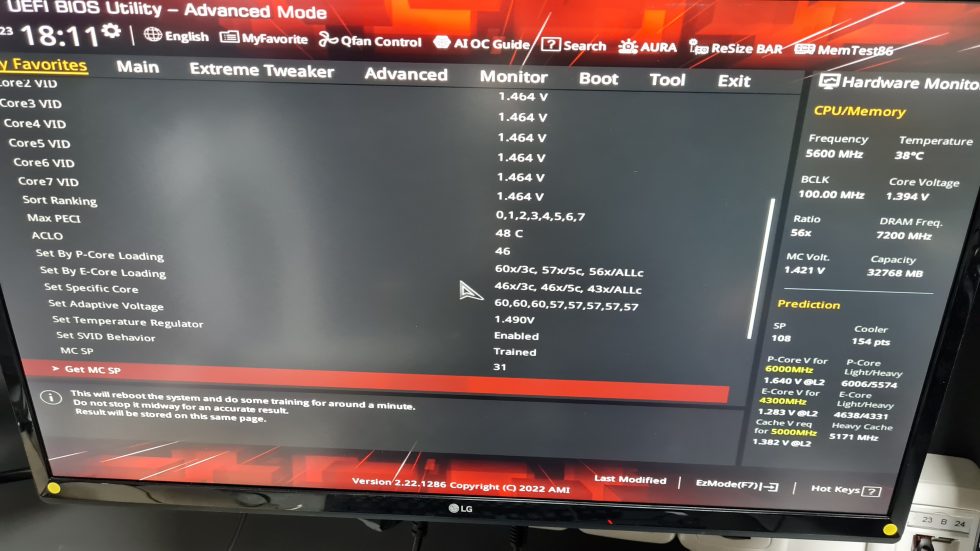

That the S(ilicon) P(rediction) of the M(emory) C(ontroller) has only a very limited significance, if at all, was already quite clear in the past tests. This time, however, we didn’t let ourselves down and actually documented the MC SP for every chip, in order to generate an approximately representative database here as well.

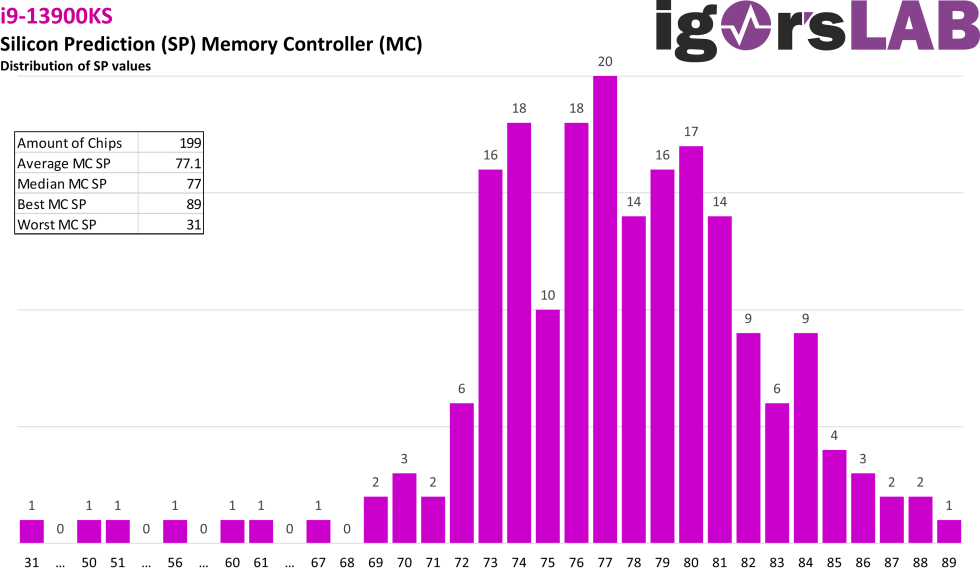

First of all, there is simply again the accumulation of a MC SP value with the corresponding number as a diagram. What is interesting here is that there are several individual downward outliers. The lowest MC SP value is an almost unbelievable 31. But even in the second and third MC SP test run, the value remains as low, except for a few single points more or less, even on a different motherboard and after cleaning the LGA pads. However, if you now think that such an MC SP 31 or 50 CPU effectively can’t run a RAM-OC at all, please read on.

Of course, it is not realistic to test all 200 CPUs for their maximum RAM-OC potential with real stability tests – the time required for this would be astronomical. However, I took a closer look at 20 of them and at least roughly tested their maximum stable RAM clock. For this purpose, y-cruncher VST is used, with which it is possible to determine quite reliably after approx. 3 loops of 2 minutes each whether a config is approximately stable or not. The Maximus Z790 Hero from Asus is again used as the basis for the tests, with 2x 16 GB SK Hynix 16 Gbit A-Die DDR5-5600 “Green Sticks” and 1.3 V SA, 1.4 V MC Voltage (VDD2), 1.55 V IVR TX Transmitter Voltage (CPU VDDQ), 1.55 V VDD and 1.55 V VDDQ with primary timings 40-50-50-118 2T as the starting configuration.

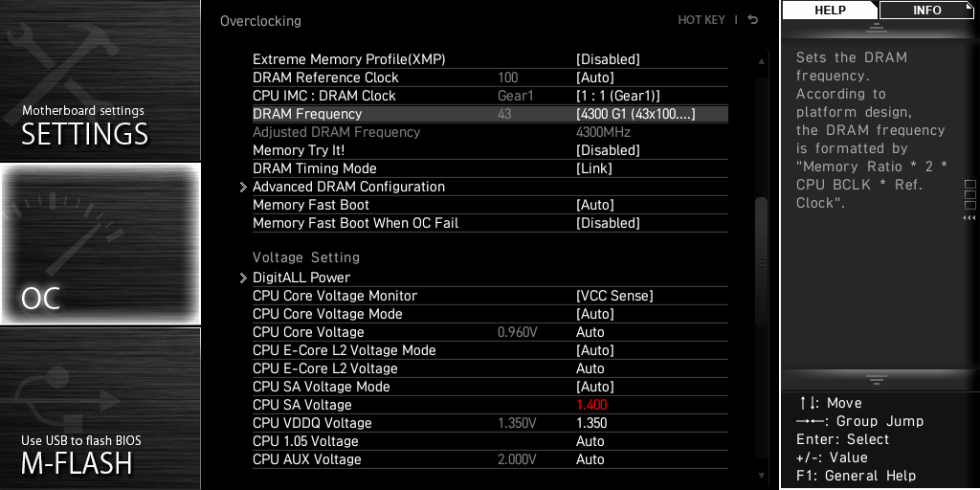

Since the MC SP effectively determines the V/F curve of the System Agent component according to shamino from the Asus R&D Department, I also tested DDR4 in Gear 1 in addition to DDR5. A particularly high clocking IMC should be able to stand out even more here due to the 1:1 coupling to the RAM, at least in theory. This was tested with an MSI PRO Z690-A motherboard, 2 x 8 GB G.Skill DDR4-4000 CL15 Samsung 8 Gbit B-Die RAM and output values of 1.4 V SA, 1.35 V CPU VDDQ, 1.55 V DRAM voltage with primary timings 19-20-20-44 2T. Since every IMC is known to have special sweet spots at these voltages, I still partially adjusted these values individually to determine the real maximum within about 45 minutes of testing per CPU.

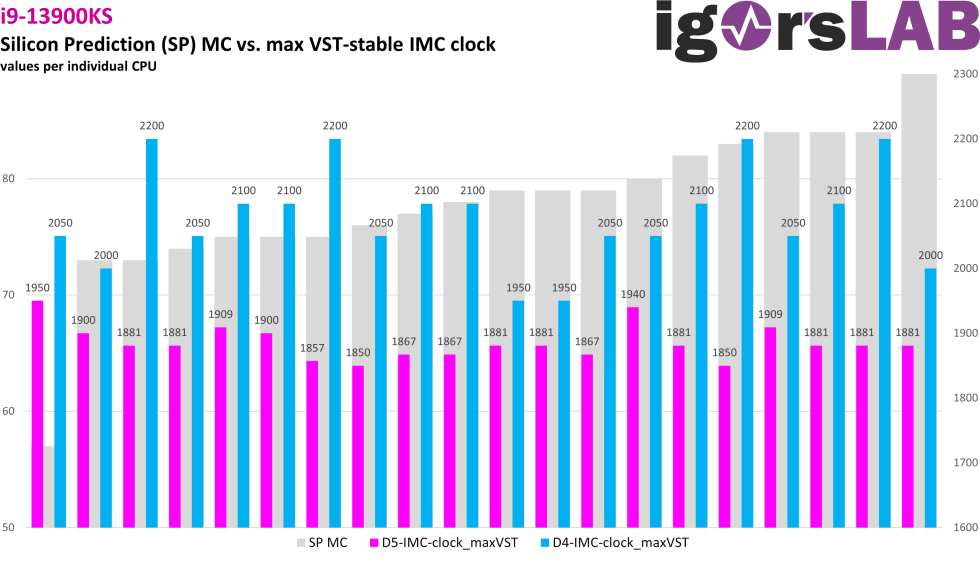

Here you can now see the MC SP, the maximum DDR4 clock and the maximum DDR5 clock, each stable in y-cruncher VST and calculated down to the actual clock of the IMC (with DDR4 in Gear 1: RAM clock/2, with DDR5 in Gear 2: RAM clock/4, because “Double Data Rate”), per CPU. The result is surprising and sobering at the same time, because there seems to be no connection at all between the MC SP and stable RAM clock. For example, the CPU with the lowest MC SP of 53 manages the highest DDR5 clock of 1950 MHz, but only a mediocre DDR4 clock. Conversely, the CPU with the highest MC SP of 89 also only manages mediocre values of 1881 or 2000 MHz.

To sum it up: The SP value for the memory controller, which Asus can evaluate on their Z790 Maximus motherboards since BIOS version 0031, has no significance at all in reality, at least according to our tests. Thus, those who have a CPU with a low MC SP should not despair and try out for themselves how high it can really be clocked on the RAM. Conversely, a high MC SP is by no means a guarantee for a stable DDR5 setup beyond 8000 Mbps.

At this point, I would like to thank Bullshooter and Sergmann, who collected the data with me, including MC SP for each chip, which meant additional time. In the end, we now know that the MC SP has no real meaning, but on the one hand this is also a valuable insight and on the other hand, perhaps other conclusions can be drawn from the collected data later.

If the RAM clock potential of a CPU can be quantified at all, it is probably not in a single simple value, as Asus has tried to do, because too many components within the CPU, with their individual voltages, play a role here. Mainboard and RAM manufacturers want to advertise high clock rates on the QVLs of their products on the one hand, but on the other hand they are dependent on the Silicon Lottery for individual CPUs so that the advertised values can also be realized in reality. As far as Intel is concerned, any RAM clock beyond JEDEC is already overclocking and not supported. RMA chaos and frustrated users are actually pre-programmed and a potential solution is as complex as it is political.

13 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Mitglied

Mitglied

Mitglied

Mitglied

Veteran

Urgestein

Neuling

Urgestein

Urgestein

Veteran

Urgestein

Veteran

Alle Kommentare lesen unter igor´sLAB Community →