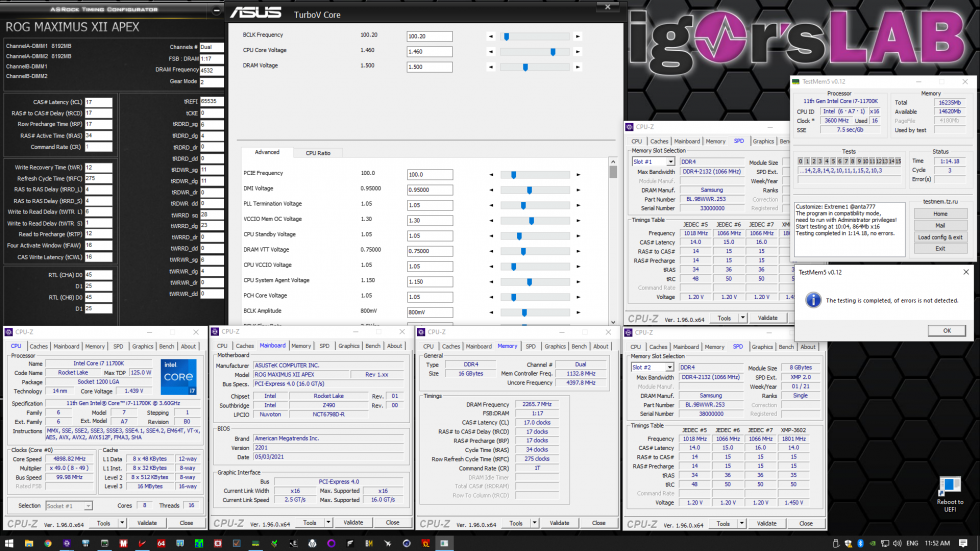

As usual, both modules are tested on both current desktop platforms, AMD Ryzen 5000 and Intel Rocket Lake, each in the XMP profile and with maximum stable overclocking. For this, the clock speed is set to DDR4-3800 on the AMD platform due to the synchronous Infinity Fabric limit and then all timings are manually tightened as much as possible. On the Intel platform, the performance scales better asynchronously with the memory controller due to the architecture, which is why the maximum stable clock rate is aimed for here first and only then the timings are tightened.

As maximum voltage for the RAM 1.5 V common for Samsung B-Die XMP kits and as stress test Testmem5 in the version 0.12 and with the profile “Extreme1@Anta777”, whereby no errors may occur, are used. The achieved overclockings show the potential of the RAM modules in the temporal context of a review and the requirements of the hardware and software listed below. With more time, knowhow and newer hardware, even better results can be achieved. The following is a complete listing of the hardware used for testing:

| Test systems | |

|---|---|

| Hardware: |

Intel platform

AMD platform

|

| Cooling: |

|

| Housing: |

|

| Periphery: |

|

| Measuring devices |

|

What’s single-rank and dual-rank together? Right, triple-rank! And so I didn’t want to miss the chance to test and overclock both kits together on the 4 DIMM mainboard of the AMD platform. This works surprisingly well and the configuration can even be run 1:1 without compromising the clock compared to the dual-rank config at 1900 MHz.

Overclocking on the AMD Ryzen platform is uncomplicated, so that almost all primary timings can be lowered despite raising the clock to DDR4-3800. Only the performance-critical primary timing tRCD cannot be lowered below 15 even with 1.5V, otherwise the first errors will occur after 10 minutes in test mem5. The rest of the timings can be set in a B-die-like fashion, with tRRD_S and tRRD_L 4, relatively low tRFC of 275, and tRDRD_SCL or tWRWR_SCL of 2. Even in dual and even triple rank, the Ryzen 5000 IMC and the B550 Aorus Pro v2 is unimpressed and can use almost the same timings as in single rank.

On the Intel platform, finding the limit is a bit more tedious due to the additional variable in the clock. Ultimately, the maximum stable clock speed is DDR4-4533 for the single-rank kit and DDR4-4266 for the dual-rank kit – beyond that, individual errors keep creeping in after several minutes, and even tweaking the DRAM VTT voltage and skews doesn’t fix them. The primary timings can be set to tCL 17, respectively 16, tRCD and tRP 17 and tRAS 34 at the clock rates mentioned.

Although this result is not absolute top class, it is quite respectable for high-end B-Die kits – after all, almost 1 GHz effective clock gain for the single-rank kit. It should also be mentioned that the Asus Maximus XII Apex board used is Rocket Lake compatible, but had not received the latest microcode updates at the time of testing, so with an up-to-date board or BIOS, it’s almost certain that a few more MHz can be extracted from the kits.

To improve the clarity of the diagrams, the following abbreviations are used:

- SR: single rank, 1 rank per channel

- DR: Dual-Rank, 2 Ranks per Channel

- TR: Triple-Rank, 3 Ranks per Channel

- 3600, 3800, 4266, 4533: The respective clock rates without “DDR4-” suffix, i.e. 1800, 1900, 2133 and 2266 MHz respectively as real clock rate

- 1T / 2T: Command Rate in Ticks

- GDM: Geardown Mode, RAM operating mode of the AMD platform with even tCL and Command Rate 1T

- Gear 1 / Gear 2: Gear ratio between RAM and IMC clock of the Intel platform, corresponds mathematically 1:1 / 2:1 of the AMD platform, Gear 2 always uses Command Rate 1T

- 1:1 / 2:1: Ratio between RAM, IMC and Infitiy Fabric clock on the AMD platform

- all-manual: completely manually set primary, secondary and tertiary timings, see screenshots above

42 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →