As usual, we first start with the synthetic benchmarks, Geekbench 3 in version 3.4.4 and the AIDA64 Cache and Memory Benchmark in version 6.33.5700. All tests were run 3 times each and then averaged. The “DDR4-” prefix has been omitted for better readability.

As expected, the configurations with high clock rates can show their advantage in the read test and consistently achieve more than 70000 MB/s. Even the Control Kit and the DJR Kit on the AMD platform with “only” DDR4-4800 can keep up here due to the tighter timings.

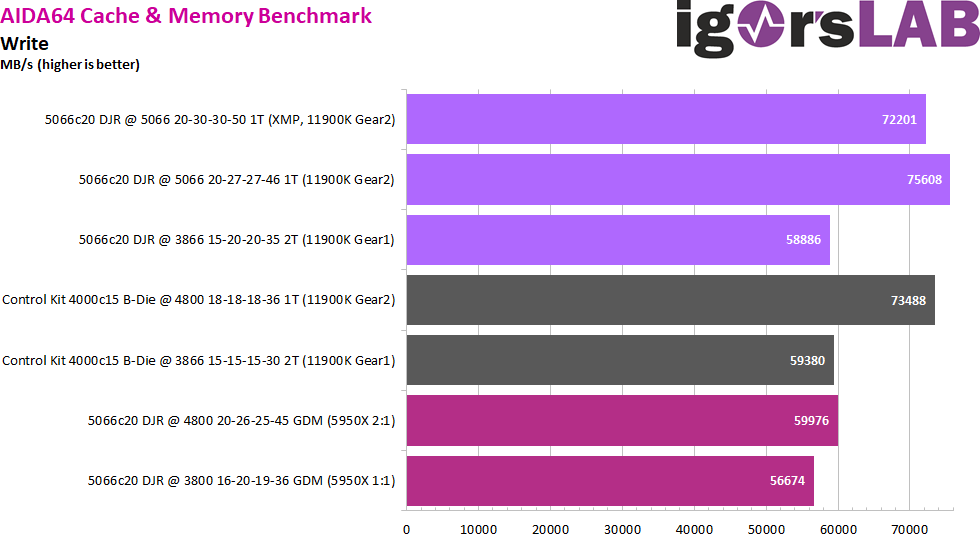

The trend continues in the write test, with the exception of the DDR4-4800 configuration on the AMD platform, where the 1:2 mode between UCLK and MCLK causes a big performance penalty. Here you can see very well that 1:2 at AMD and Gear 2 at Intel are not really the same.

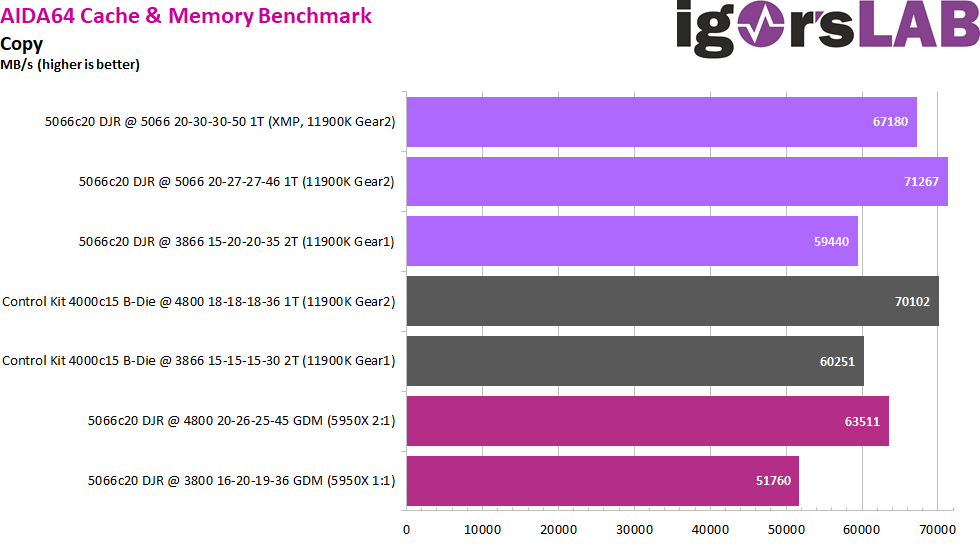

The Copy test is, as usual, a compromise between Read and Write and therefore looks similar in terms of results. As in the Write test, the kit from today’s test with the manually tightened primary timings is a close first here.

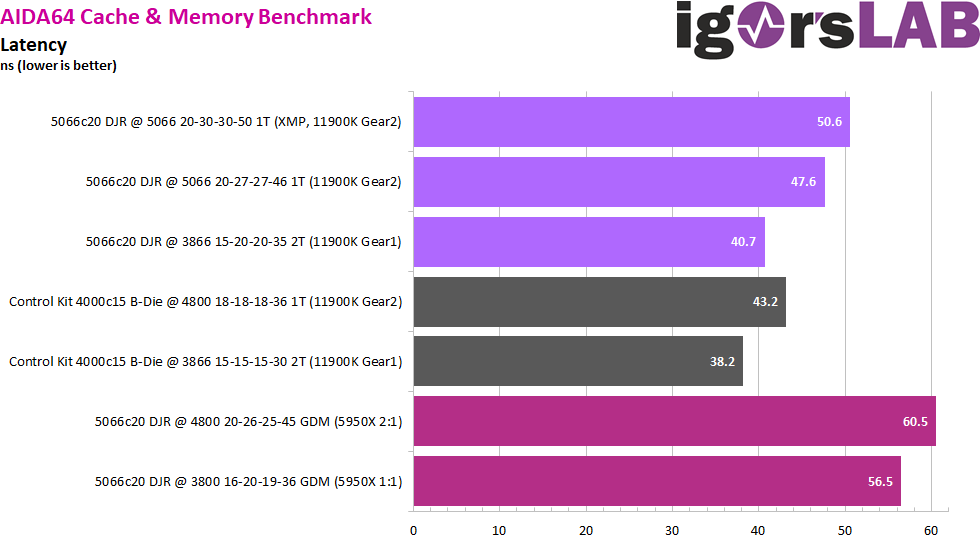

In the latency test, the disadvantage of the DJR ICs with higher tRCD, tRP and tRAS is noticeable, which is reflected in 2-3 ms poorer latencies compared to the control kit.

In the Geekbench 3 Multi-Core Memory Score, which has proven to be a reliable indicator for most real-world applications, the DJR kit from today’s test is just behind the B-Die control sample. But even with complete XMP timings, the kit still manages well over 10000 points on the Rocket Lake platform. Not bad for plug and play.

10 Antworten

Kommentar

Lade neue Kommentare

Mitglied

Mitglied

Urgestein

Veteran

Urgestein

Mitglied

Mitglied

Veteran

Alle Kommentare lesen unter igor´sLAB Community →