What does dynamic pSLC cache actually mean?

Let’s now move on to a somewhat more technical detail that most people are probably not fully aware of. A lot has already been written about pSLC cache, so there’s no need to go through it again in detail, at most as a little refresher. Here we go…

To increase the write speed, the so-called “pseudo-SLC cache” (pSLC) is often used in consumer products, although it can now also be found in various industrial solutions. For this purpose, part of the NAND capacity is configured as SLC memory, in which only one bit per cell is stored. Accordingly, this memory can be written and read very quickly. As it is not dedicated, i.e. not real SLC memory, it is called pseudo SLC. Such a cache can be used for all memory types that store several bits per flash cell, i.e. three bits as in the case of TLC. The pSLC cache also uses a significantly higher voltage for the one bit, which offers a certain level of security and is therefore better than Fast Page.

The use of pSLC cache offers a speed advantage, especially when the storage medium is not busy with read or write accesses between writing large amounts of data. These idle times are used by the storage medium to move data from the cache to the QLC area.

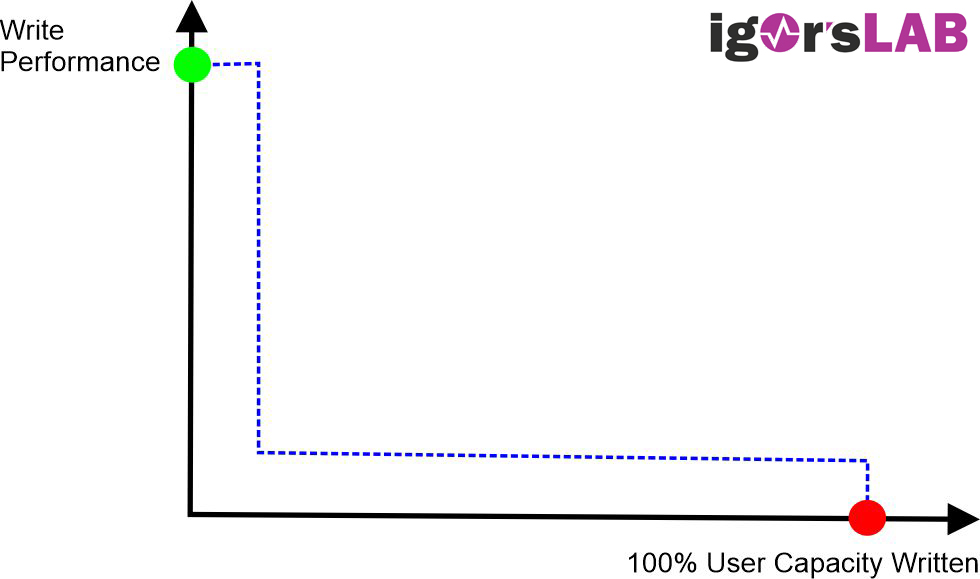

But everyone knows the disadvantages of the pSLC. When the fast pSLC cache is full, the speed drops significantly, as further write accesses to the storage medium must first free up the pSLC by moving older data from the cache to the QLC memory.

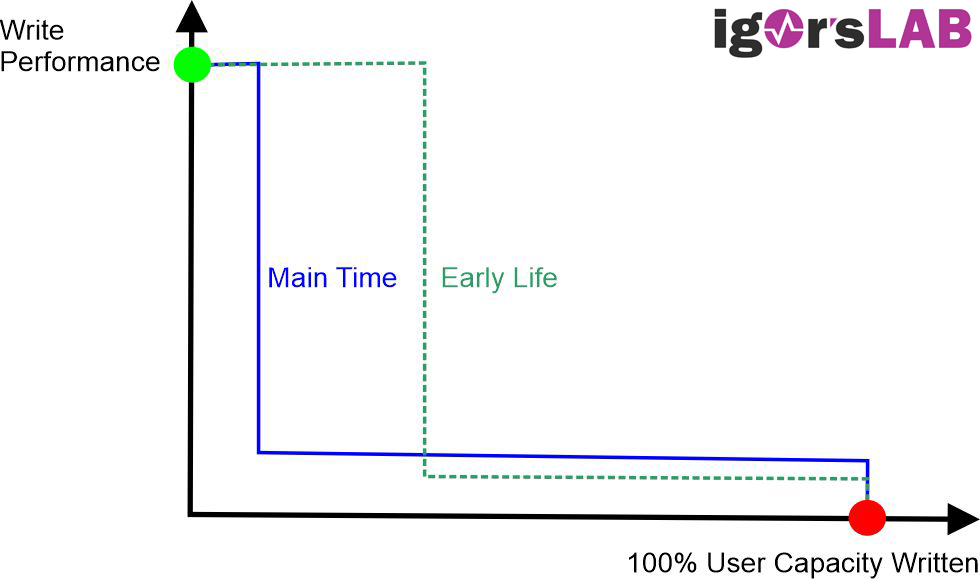

But what does “dynamic pSLC cache” actually mean? Dynamic pSLC cache has now also found its way into industrial storage solutions, but only with very severe restrictions. In contrast to the static pSLC cache, up to 100% of the NAND flash is used dynamically as a pSLC cache, depending on how full the storage medium is. The cache can therefore comprise up to 1/4 of the total memory size

However, the write speed of the storage medium depends not only on the amount of data that is written without interruption, but also on the fill level of the memory. And this is precisely what makes the write speed in the life cycle difficult to predict.

Although NAND flash manufacturers advise against dynamically changing the configuration of flash blocks as pSLC or QLC memory for reasons of reliability, in the consumer sector, where temperature windows are not so important, this is viewed somewhat more relaxed.

All manufacturers of dynamic NAND storage media, including YMTC, permanently switch back to QLC mode after a specified maximum number of program and erase cycles. Before this, the storage medium achieves the best values, especially for short write operations that do not require the entire capacity. After a certain period of use, however, the medium is permanently slowed down and this should never be ignored. The controller used here is also quite good at dynamically changing the configuration of flash blocks, but it cannot outwit physics either.

When you will reach the end of the great cache performance is a matter of uncertainty. The cache is specified with around 460 GB, which also makes sense in purely mathematical terms with 2 TB QLC. Then the glory comes to an end and you are only at a mediocre SATA level. In practice, you will hardly be able to manage this, but it’s better not to fill it up in one go and perhaps more often.

11 Antworten

Kommentar

Lade neue Kommentare

Veteran

Veteran

Mitglied

Urgestein

Moderator

Urgestein

Mitglied

Urgestein

Moderator

Veteran

Mitglied

Alle Kommentare lesen unter igor´sLAB Community →