Guest performance on AM5

Alternatively, you could do it like AMD, where the RAM training has no mood swings and DDR5 also trains reproducibly at the limits of the IMC. I had some fun and simply plugged the Corsair Dominator Titantium Kit with DDR5-8000 XMP profile into an AM5 board. Although XMP is actually intended for Intel platforms and EXPO is designed for AMD, both standards are technically based on the same solution with the same predefined RAM timings. And this is precisely why the Asus Crosshair X670E Gene can also load the XMP profile via “DOCP” without any problems. This is also a 2-DIMM board and virtually the Asus equivalent for AM5 to the Z790 Apex for LGA1700. It is only important that a reasonably up-to-date BIOS / AGESA is used that supports the high clock rates in 1:2 mode, such as the 1807 release here.

And lo and behold, it is simply always stable! AMD also has “MRC Fastboot”, only here it is called “Memory Context Restore”. If you deactivate this, the system retrains with every restart and you can evaluate the reliability of the RAM training through stress tests with intermediate reboots. All timings are also respected on this platform, including tWR, which Asus unfortunately does not do on the Intel board. Of course, the subtimings are also much too loose here, as with Intel CPUs, and the performance is therefore not as tingling as it could be with this clock rate. But at least the system is reproducibly stable and that is the prerequisite for us to be able to think about performance tuning in the first place!

To what extent DDR5-8000 on AM5 makes sense is another debate, especially with an X3D CPU like this one. FCLK 2000, UCLK 2000, MCLK 4000 reads quite nicely and if you think of Ryzen 5000 times, you could expect more performance through “synchronous” clock rates, but unfortunately with Ryzen 7000 the Infinity Fabric is too big (small) a bottleneck for the RAM bandwidth to be fully utilized. AMD has a bottleneck problem between cores and RAM controller. Intel has a tuning problem between RAM controller and RAM. If only you could just take the best of both worlds..

What I want to show with the guest performance on AM5: The stability problem here is not due to Corsair’s Dominator Titanium RGB DDR5-8000 kit. If you combine this with an AMD CPU, you can actually run 8000 Mbps in a reproducible and stable manner. With an Intel platform, stability at such high clock rates is unfortunately often a game of chance. This problem has existed since the first DDR5 CPUs of the 12th generation, but with advances in DRAM technology and increasing clock rates, the issue is becoming more and more explosive. This is probably the reason why Corsair is not advertising the kit as DDR5-8200, even though the XMP profile is already included in the SPD. I wouldn’t be surprised if the manufacturers’ R&D departments have been racking their brains about this for some time.

Overclocking

I have now identified DDR5-7800 as the effective limit of my Intel test system and, based on this, have tightened the timings and increased the voltage slightly. 1.6 V VDD is the only increased voltage; even VDDQ, VDD2 and CPU VDDQ can remain unchanged from the XMP profile, at 1.4 V. The fact that the VDD and VDDQ voltages are then no longer synchronous is not a problem as long as the difference is not more than 300 mV, at least according to official documentation from DDR5 manufacturers.

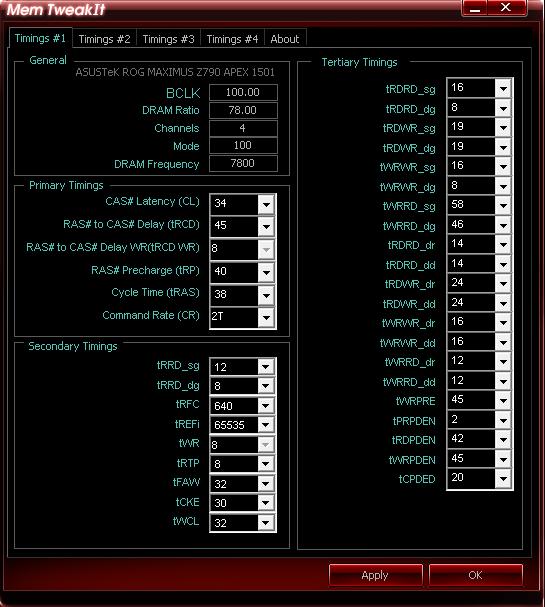

tCL can now be reduced to 34 by the additional VDD voltage. I also tried tCL 32, but that would probably require > 1.7 V and that was too extreme for me, even with a fan on the modules. The remaining timings can be significantly tightened as is typical for Hynix, e.g. tRDRD_sg/dg and tWRWR_sg/dg to 16/8 each. These significantly increase the bandwidth in particular and always work effectively with SK Hynix-based DDR5 kits. In some cases, these can be tightened even further, but often no performance difference can be measured. Also tRRD_sg/dg and tFAW can be tightened significantly, but the 24 Gbit ICs seem to have a minimum value of tRRD_sg 12, while 16 Gbit ICs could often operate a value of 8 stably.

to be honest, I simply overlooked tCKE after weeks of testing, but performance-wise the timing is effectively irrelevant anyway. tRFC_pb is not shown on the first page of MemTweakIt – this timing is set to 576. For a complete list of the adjusted timings, please refer to the screenshots.

In general, it is noticeable that SK Hynix 24 Gbit M-Die has to run slightly looser timings than 16 Gbit A-Die at the same clock rate. Nevertheless, there is currently no other IC manufacturer that can even come close to keeping up with the ratio of clock rate to timings here.

49 Antworten

Kommentar

Lade neue Kommentare

Urgestein

Urgestein

Veteran

Urgestein

Veteran

Veteran

Veteran

Urgestein

Urgestein

Urgestein

Urgestein

Veteran

Urgestein

Veteran

Urgestein

Urgestein

Veteran

Urgestein

Urgestein

Alle Kommentare lesen unter igor´sLAB Community →