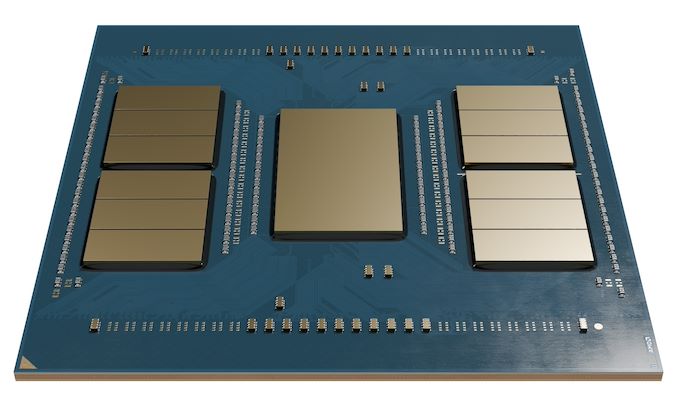

Die kommende AMD Ryzen Threadripper 9000 CPU, die auf der Zen 5-Kernarchitektur basiert, wurde kürzlich in einem Versandkatalog entdeckt, berichtet NBD. Der Prozessor, der den Codenamen „Shimada Peak“ trägt, soll über bis zu 96 Kerne und 192 Threads verfügen. Diese Konfiguration besteht aus 12 Chiplet-Dies (CCDs), von denen jedes 8 Kerne und 32 MB L3-Cache […] (read full article...)

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Internetseiten nicht korrekt angezeigt werden.

Du solltest ein Update durchführen oder einen alternativen Browser verwenden.

Du solltest ein Update durchführen oder einen alternativen Browser verwenden.

Shimada Peak aufgetaucht: AMDs neue HEDT-CPU mit 96 Kernen

- Themenstarter Redaktion

- Beginndatum

OldMan

Veteran

Das wir ein sehr interessantes Monster! Mit 12 CCD's bin ich mal gespannt wie das in der Praxis funktioniert. Der L3 ist aber mit den angeblichen 32 MB nicht gewachsen, schade eigentlich, da hätte ich mir etwas mehr (das doppelte wäre nett gewesen) erhofft. Mal abwarten wie er sich in der freien Wildbahn entwickelt!

Midnight Angel

Veteran

...wobei ich den Sinn von 96 Kernen maximal beim TR Pro sehe - die vier Speicherkanäle des 'normalen' TR könnten die Kerne ein klein wenig verhungern lassen...

OldMan

Veteran

Da gebe ich Dir recht, der Pro hat ja octachanel. Die normalen wird es eh nicht mit 96 Kernen geben, da wird sich nicht viel zum Ist-Stand tun. Da gibt es die 96Kerne ja auch nur beim Pro....wobei ich den Sinn von 96 Kernen maximal beim TR Pro sehe - die vier Speicherkanäle des 'normalen' TR könnten die Kerne ein klein wenig verhungern lassen...

Dr4x

Mitglied

- Mitglied seit

- Okt 13, 2023

- Beiträge

- 83

- Bewertungspunkte

- 60

- Punkte

- 17

Und was genau erhoffst du dir vom doppelten L3 Cache? Was soll dir dieser jetzt genau bringen?Das wir ein sehr interessantes Monster! Mit 12 CCD's bin ich mal gespannt wie das in der Praxis funktioniert. Der L3 ist aber mit den angeblichen 32 MB nicht gewachsen, schade eigentlich, da hätte ich mir etwas mehr (das doppelte wäre nett gewesen) erhofft. Mal abwarten wie er sich in der freien Wildbahn entwickelt!

eastcoast_pete

Urgestein

- Mitglied seit

- Jun 25, 2020

- Beiträge

- 1.796

- Bewertungspunkte

- 1.125

- Punkte

- 112

Es sind aber auch 32 MB L3 pro CCD, dh 384 MB (12 CCDs) insgesamt, also gleichviel wie beim derzeitigen 96 Kern Pro TR.Das wir ein sehr interessantes Monster! Mit 12 CCD's bin ich mal gespannt wie das in der Praxis funktioniert. Der L3 ist aber mit den angeblichen 32 MB nicht gewachsen, schade eigentlich, da hätte ich mir etwas mehr (das doppelte wäre nett gewesen) erhofft. Mal abwarten wie er sich in der freien Wildbahn entwickelt!

Wenn irgendwas hier die theoretische Leistung begrenzt, ist es die Zahl der Speicherkanäle, und auch nur dann, wenn AMD dieses Monster auch als "TR" (ohne Pro) rausbringt; die TRs haben ja "nur" 4. Für die Pro Modelle erwarte ich, daß AMD die Konfiguration mit 8 Speicherkanälen beibehält.

Aber, in beiden Fällen hätten die Zen5 TRs sehr viel mehr Compute Leistung als ich wirklich brauche.

8j0ern

Urgestein

- Mitglied seit

- Mrz 4, 2021

- Beiträge

- 2.911

- Bewertungspunkte

- 957

- Punkte

- 113

Bei den EPYC CPU haben die 96 Kerne 192 Threads vom Zen5c 12 Channel IMC.

Die laufen wiederum auch zu zweit auf einem Mainboard.

Die laufen wiederum auch zu zweit auf einem Mainboard.

Onkel-Föhn

Veteran

- Mitglied seit

- Okt 23, 2020

- Beiträge

- 112

- Bewertungspunkte

- 64

- Punkte

- 28

- Alter

- 52

- Standort

- bei Kempten im Allgäu

Sieh Dir einfach an, was die "aufgebohrten" Caches bei EPYC bringen/leisten (ZEN 5 vs. ZEN 4) !Und was genau erhoffst du dir vom doppelten L3 Cache? Was soll dir dieser jetzt genau bringen?

Bergamo geschlagen: Der neue Turin Prozessor ist doppelt so schnell | igor´sLAB

AMD hat kurz vor der Veröffentlichung seiner 5. Generation der EPYC-Prozessoren, bekannt als “Turin”, neue Leistungsdaten präsentiert. Diese Chips basieren auf der Zen 5-Architektur und zeigen im…

OldMan

Veteran

mehr L3 Chache bedeutet mehr Platz für Programme die direkt im L3 laufen. Zugegeben, das sind Spezialanwendungen aber genau damit beschäftige ich mich eben. Somit wäre hier mehr echt von Vorteil.Und was genau erhoffst du dir vom doppelten L3 Cache? Was soll dir dieser jetzt genau bringen?