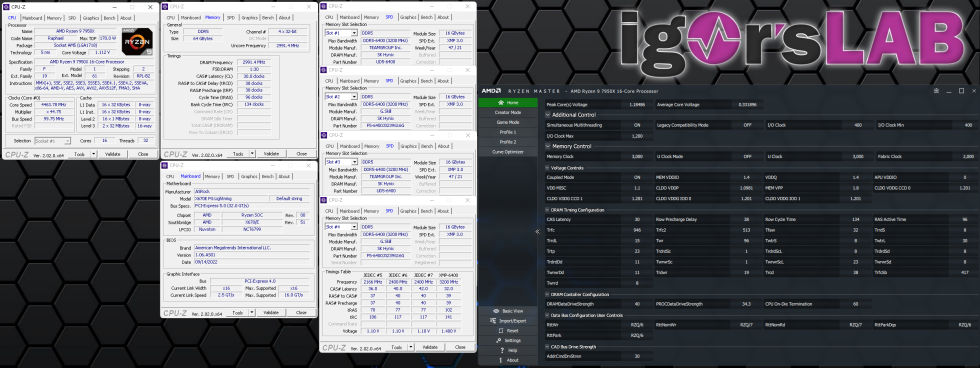

6000 CL30 EXPO 1:1 5H16M DR, 2000 IF – Vollbestückung

Die DDR5-6000 CL30 Konfiguration gibt es nun noch ein weiteres mal in doppelter Ausführung, also mit 4 RAM Modulen, statt wie üblich 2. Ja, mit X670 und Zen 4 lassen sich 64 GB DDR5 RAM mit 6000 Mbps tatsächlich stabil betreiben. Aufgrund der Dual-Channel Architektur stellt diese Konfiguration dann Effektiv Dual-Channel dar und ist entsprechend in den Diagrammen gekennzeichnet. Damit sehen wir dann also auch gleich, ob Dual-Rank im Vergleich zu Single-Rank einen vertretbaren Performance-Zuwachs bringt.

Neben dem G.Skill 6400 CL32 Kit kommt hierfür noch ein Teamgroup 6000 CL40 Kit zum Einsatz. Beide Kits verwenden zwar die selben Hynix M-Die Speicherbausteine und lassen sich trotz ihrem unterschiedlichen Platinen-Design problemlos miteinander kombinieren.

6000 CL30 EXPO 1:1 5H16M SR, 2167 IF – Maximiertes Infinity Fabric

Hierbei handelt es sich um ein letztes Mal um die Single-Rank Config mit 6000 Mbps und EXPO Timings, diesmal aber mit voll ausgereiztem Infinity Fabric Takt bei 2167 MHz. So können wir ein weiteres mal sehen, wie viel Performance die schnellere Verbindung zwischen IO-Die und Chiplets wirklich mit sich bringt, und zudem, ob sich dieses Verhalten zwischen JEDEC und EXPO RAM-Einstellungen unterscheidet.

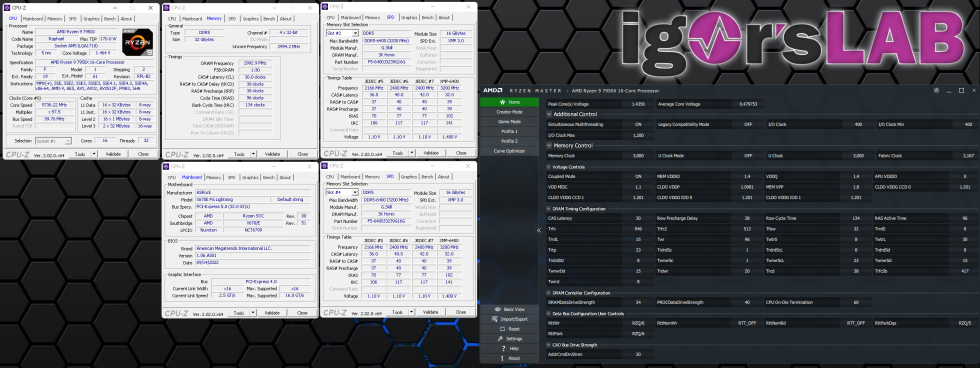

6400 CL32 * 1:1 5H16M SR, 2133 IF – Komplett optimierter Single-Rank Hynix M-Die

Jetzt geht es endlich an die manuell optimierten Konfigurationen, wobei die maximale erreichte Taktrate von 6400 Mbps leider etwas niedriger ist als ich es mir gewünscht hätte. Hier hat entweder der frühe AGESA Code noch ein wenig Luft nach oben oder mein Mainboard hat hier ein hartes Limit. Da sich dieses Limit aber auch mit nur einem einzelnen RAM Modul in Slot B2 bemerkbar macht, tendiere ich zu ersterem. Meldungen von Testern mit Mainboards anderer Hersteller bestätigten mir ebenfalls ein hartes Limit von aktuell 6400 – 6600 Mbps, zumindest bei normalen Temperaturen.

DDR5-6400 vorausgesetzt wurden dann alle Timings gestrafft und das wohl gemerkt noch immer im 1:1 Modus bei unveränderten Spannungen. Leider scheint es noch einen Bug in der Ryzen Master Software zu geben, sodass die Timings hier nicht mehr korrekt angezeigt werden. Entsprechend müsst ihr ab hier bitte mit Screenshots aus dem BIOS Vorlieb nehmen.

Durch das höhere Datenaufkommen scheint nun allerdings das Infinity Fabric stärker belastet zu werden, wodurch hier ein Schritt weniger und damit nur noch 2133 MHz stabil zu betreiben sind. Auch mit höheren Spannungen bei SOC, VDDG etc. lässt sich mit derart schnellem RAM 2167 MHz auf dem FCLK nicht mehr stabilisieren. Manchmal bootet das System noch, landet aber kurze Zeit später immer im Bluescreen of Death.

6400 CL32 * 1:1 5H16M DR, 2133 IF – Komplett optimierter Dual-Rank Hynix M-Die

Das ganze gibt es entsprechend Analog noch einmal in Vollbesetzung mit 4x 16 GB, wobei hier entsprechend die Tertiärtimings endend auf Dd (different DIMM) relevant werden und nicht länger auf 1 minimiert werden können. Zudem benötigt die doppelte Anzahl an Ranks etwas mehr SOC Spannung, hier 1,4 V, wobei dies laut mehreren Quellen auch noch im sicheren Bereich ist.

6400 CL36 * 1:1 5S16B SR, 2167 IF – Takt-Deckel als Rettung für Samsungs DDR5?

In unseren DDR5-Test mit Kits, die Samsungs 16 Gbit B-Die Speicher-ICs verwenden, war deren relativ geringes Taktpotential immer ein großes Manko. Aber wie verhalten sich die ICs denn nun, wenn der Takt bei 6400 Mbps vorgegeben ist und die Timings letztendlich die maßgebliche Eigenschaft sind? Vor allem die strafferen tRCD, tRP und tRRD Timings dürften hier den Samsung ICs zu Gute kommen.

Zudem lässt sich mit leicht erhöhten Spannungen auch 2167 MHz auf dem Infinity Fabric wieder stabilisieren – weniger ist eben manchmal auch wieder mehr. Neben 1,4 V SOC kommen hier 1,15 V VDD Misc, 1,25 V VDDG CCD, 1,25 V VDDG IOD und 1,15 V VDDP Spannung zum Einsatz.

Übrigens habe ich auch Hynix 16 Gbit A-Die getestet, dieser verhält sich aber genauso wie Hynix 16 Gbit M-Die und lässt sich auch nicht höher als 6400 Mbps takten. Zudem verhält sich Micron 16 Gbit RevA mit Zen 4 sich genauso wie mit Intel Alder Lake und stellt ab DDR5-5800 den Dienst ein. Entsprechend gibt es hierzu vorerst keine Konfigurationen und Ergebnisse, bis sich dies in kommenden AGESA Updates ggf. ändert.

- 1 - Was ist neu bei Ryzen 7000?

- 2 - Test-Setup und Software-Tools

- 3 - BIOS Einstellungen (1/2) – DDR5

- 4 - BIOS Einstellungen (2/2) – CPU-OC und sonstige

- 5 - Getestete Konfigurationen (1/2)

- 6 - Getestete Konfigurationen (2/2)

- 7 - Synthetics (1/2) – LinpackXtreme, AIDA64 und Geekbench 3

- 8 - Synthetics (2/2) – SuperPi 32M, PyPrime 2.0 2B, Timespy CPU

- 9 - Gaming QHD, FHD – ACC, CSGO, SoTR

- 10 - Zusammenfassung und Empfehlungen

221 Antworten

Kommentar

Lade neue Kommentare

Veteran

Veteran

Mitglied

Urgestein

1

Urgestein

Veteran

Urgestein

Urgestein

Veteran

Urgestein

Veteran

Urgestein

Urgestein

Urgestein

Neuling

Mitglied

Mitglied

Alle Kommentare lesen unter igor´sLAB Community →